Product Summary

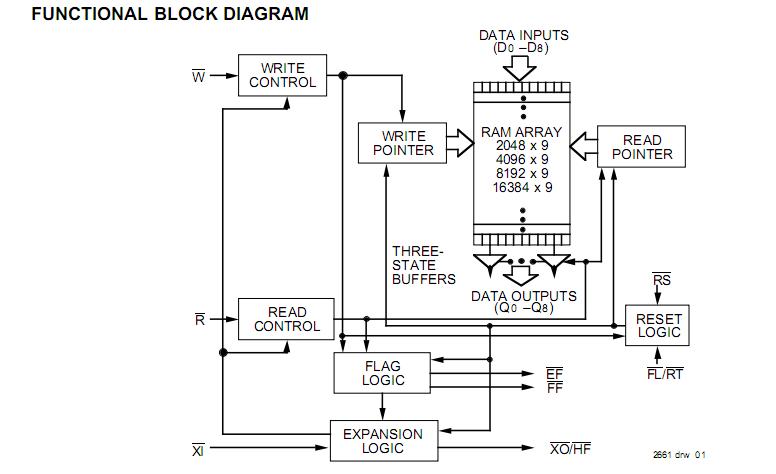

The IDT7204LA35J is a dual-port memory buffer with internal pointers that load and empty data on a firstin/first-out basis. The IDT7204LA35J uses Full and Empty flags to prevent data overflow and underflow and expansion logic to allow for unlimited expansion capability in both word size and depth. Data is toggled in and out of the device through the use of the Write (W) and Read (R) pins. The IDT7204LA35J 9-bit width provides a bit for a control or parity at the user’s option. It also features a Retransmit (RT) capability that allows the read pointer to be reset to its initial position when RT is pulsed LOW. A Half-Full Flag is available in the single device and width expansion modes.

Parametrics

IDT7204LA35J absolute maximum ratings: (1)Terminal Voltage with Respect to GND: –0.5 to + 7.0 V; (2)Operating Temperature: 0 to +70 ℃; (3)Temperature Under Bias: –55 to +125 ℃; (4)Storage Temperature: –55 to + 125 ℃; (5) DC Output Current: 50 mA.

Features

IDT7204LA35J features: (1)First-In/First-Out Dual-Port memory; (2)2048 x 9 organization (IDT7203); (3)4096 x 9 organization (IDT7204); (4)8192 x 9 organization (IDT7205); (5)16384 x 9 organization (IDT7206); (6)High-speed: 12ns access time; (7)Low power consumption: Active: 770mW (max.), Power-down: 44mW (max.); (8)Asynchronous and simultaneous read and write; (9)Fully expandable in both word depth and width; (10)Pin and functionally compatible with IDT720X family; (11)Status Flags: Empty, Half-Full, Full; (12)Retransmit capability; (13)High-performance CMOS technology.

Diagrams

|

IDT7005 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

IDT7005L |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

IDT7005L15J |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

|

IDT7005L15J8 |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

|

IDT7005L15JG |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

|

IDT7005L15JG8 |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))