Product Summary

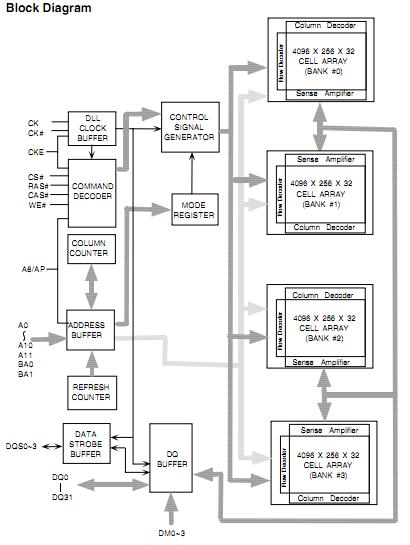

The EM6A9320BI-4MG is a high-speed CMOS double data rate synchronous DRAM containing 128 Mbits. The EM6A9320BI-4MG is internally configured as a quad 1M x 32 DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CK). Data outputs occur at both rising edges of CK and CK#. Read and write accesses to the SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence.

Parametrics

EM6A9320BI-4MG absolute maximum ratings: (1)VIN, VOUT, Input, Output Voltage: - 0.3 ~ VDDQ+0.3 V; (2)VDD, VDDQ, Power Supply Voltage: -0.3 ~ 3.6 V; (3)TA, Ambient Temperature: 0~70℃; (4)TSTG, Storage Temperature: - 55~150℃; (5)TSOLDER, Soldering Temperature (10s): 260℃; (6)PD, Power Dissipation: 2.0 W; (7)IOUT, Short Circuit Output Current: 50 mA.

Features

EM6A9320BI-4MG features: (1)Fast clock rate: 250/200/166 MHz; (2)Differential Clock CK & CK# input; (3)4 Bi-directional DQS. Data transactions on both edges of DQS (1DQS / Byte); (4)DLL aligns DQ and DQS transitions; (5)Edge aligned data & DQS output; (6)Center aligned data & DQS input; (7)4 internal banks, 1M x 32-bit for each bank; (8)Programmable mode and extended mode registers; (9)Full page burst length for sequential type only; (10)Start address of full page burst should be even; (11)All inputs except DQ’s & DM are at the positive edge of the system clock; (12)No Write-Interrupted by Read function; (13)4 individual DM control for write masking only; (14)Auto Refresh and Self Refresh; (15)4096 refresh cycles / 32ms.

Diagrams

|

EM6A6165TS |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EM6A8160TSA |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EM6A9160 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EM6A9160TS/BN |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EM6A9320 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EM6A9320BI |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))