Product Summary

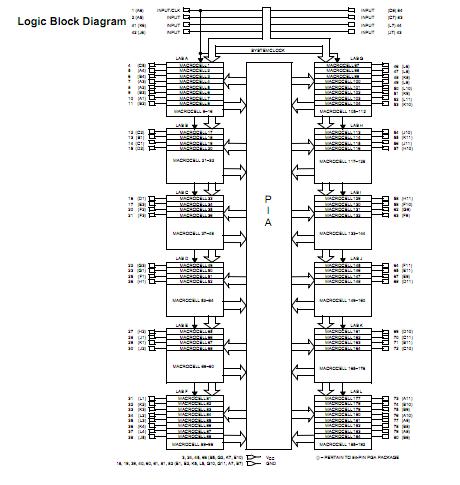

The CY7C341B-25JC is an Erasable Programmable Logic Device (EPLD) in which CMOS EPROM cells are used to configure logic functions within the device. The MAX architecture is 100% user-configurable, allowing the CY7C341B-25JC to accom-modate a variety of independent logic functions.

Parametrics

CY7C341B-25JC absolute maximum ratings: (1)Storage Temperature: -65 to +135℃; (2)Ambient Temperature with Power Applied: –65 to +135℃; (3)Maximum Junction Temperature (Under Bias): 150℃; (4)Supply Voltage to Ground Potential: -2.0V to +7.0V; (5)DC Output Current, per Pin: -25 mA to +25 mA; (6)DC Input Voltage: -2.0V to +7.0V.

Features

CY7C341B-25JC features: (1)192 macrocells in 12 logic array blocks (LABs); (2)Eight dedicated inputs, 64 bidirectional I/O pins; (3)Advanced 0.65-micron CMOS technology to increase performance; (4)Programmable interconnect array; (5)384 expander product terms; (6)Available in 84-pin HLCC, PLCC, and PGA packages.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

CY7C341B-25JC |

|

IC EPLD 192MACROCELL 25NS 84PLCC |

Data Sheet |

Negotiable |

|

||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|

CY7C006 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-15AXC |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-15AXCT |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-20AC |

|

IC SRAM 16KX8 DUAL 64LQFP |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-20AXC |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))