Product Summary

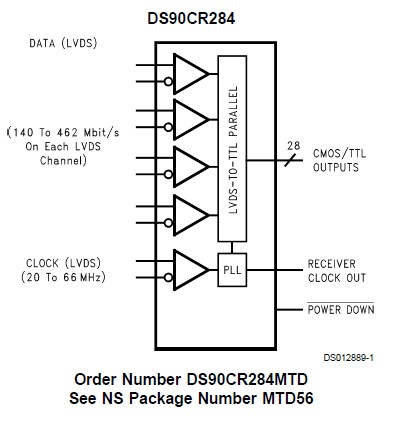

The DS90CR284MTD transmitter converts 28 bits of CMOS/TTL data into four LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link. Every cycle of the transmit DS90CR284MTD clock 28 bits of input data are sampled and transmitted. The DS90CR284 receiver converts the LVDS data streams back into 28 bits of CMOS/TTL data. At a transmit clock frequency of 66 MHz, 28 bits of TTL data are transmitted at a rate of 462 Mbps per LVDS data channel. Using a 66 MHz clock, the data throughput is 1.848 Gbit/s (231 Mbytes/s). The multiplexing of the data lines provides a substantial cable reduction. Long distance parallel single-ended buses typically require a ground wire per active signal (and have very limited noise rejection capability). Thus, for a 28-bit wide data bus and one clock, up to 58 conductors are required. With the Channel Link chipset as few as 11 conductors (4 data pairs, 1 clock pair and a minimum of one ground) are needed. The DS90CR284MTD provides a 80% reduction in required cable width, which provides a system cost savings, reduces connector physical size and cost, and reduces shielding requirements due to the cable smaller form factor. The DS90CR284MTD inputs can support a variety of signal combinations. For example, 7 4-bit nibbles or 3 9-bit (byte +parity) and 1 control.

Parametrics

DS90CR284MTD absolute maximum ratings: (1)Supply Voltage (VCC): -0.3V to +6V; (2)CMOS/TTL Input Voltage: -0.3V to (VCC + 0.3V); (3)CMOS/TTL Ouput Voltage: -0.3V to (VCC + 0.3V); (4)LVDS Receiver Input Voltage: -0.3V to (V CC + 0.3V); (5)LVDS Driver Output Voltage: -0.3V to (VCC + 0.3V); (6)LVDS Output Short Circuit: Duration Continuous; (7)Junction Temperature: +150℃; (8)Storage Temperature Range: -65℃ to +150℃; (9)Lead Temperature(Soldering, 4 sec.): +260℃.

Features

DS90CR284MTD features: (1)66 MHz clock support; (2)Up to 231 Mbytes/s bandwidth; (3)Low power CMOS desig(< 610 mW); (4)Power Dowmode (< 0.5 mW total); (5)Up to 1.848 Gbit/s data throughput; (6)Narrow bus reduces cable size and cost; (7)290 mV swing LVDS devices for low EMI; (8)PLL requires no external components; (9)Low profile 56-lead TSSOP package; (10)Rising edge data strobe; (11)Compatible with TIA/EIA-644 LVDS Standard.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

DS90CR284MTD/NOPB |

|

IC RCVR 28BIT CHAN LINK 56TSSOP |

Data Sheet |

Negotiable |

|

||||

|

DS90CR284MTDX/NOPB |

|

IC TXRX 28BIT CHAN LINK 56TSSOP |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))